## The Amiga 3000+ System Specification

An enhanced Amiga 3000 family computer

Document Revision 0.6

1991 DevCon Release

by Dave Haynie

July 17, 1991 Copyright © 1991 Commodore-Amiga, Inc.

## IMPORTANT INFORMATION

### **This Document Contains Preliminary Information**

The Amiga 3000+ computer described in this document is currently a work in progress. While this is an honest attempt to specify the A3000+ computer, it is still very preliminary in nature and subject to possible errors and omissions. Additionally, the specification of the A3000+ itself is still subject to possible change at this stage in the design cycle.

Commodore Technology reserves the right to correct any mistake, error, omission, or viscious lie. Corrections will be published as updates to this document, which will be released as necessary in as developer-friendly a manner as possible. Revisions will be tracked via the revision number that appears on the front cover.

This document does not constitute a guarantee that Commodore will build or offer the A3000+, as described herein or in any other form, for sale at any given time, place, cost, etc. Nor is this a guarantee that Commodore will ever release anything called "Amiga 3000+". This is simply the design and working name for a prototype next generation Amiga 3000 class computer as of the cover date.

All information herein is Copyright © 1991 by Commodore International Services Corporation, and may not be reproduced in any form without written permission.

Most of the text in Chapter 3, and the Lisa chip itself, were created by Bob Raible. Without Bob, and the other "AA" guys, Bill Thomas and Chingtao Shen, there would be no A3000+.

## $TABLE \ OF \ CONTENTS$

| CHAPTER | 1     | INTRODUCTION                      |      |

|---------|-------|-----------------------------------|------|

|         | 1.1   | Basic Description                 | 1-1  |

|         | 1.2   | Memory Organization               |      |

| CHAPTER | 2     | MAIN SYSTEM CONTROLS              |      |

|         | 2.1   | Gary+                             | 2-1  |

|         | 2.1.1 | Bus Timeout Support               |      |

|         | 2.1.2 | Reset Control                     | 2-3  |

|         | 2.1.3 | Gary+ ID                          | 2-3  |

|         | 2.2   | RAMSEY                            | 2-3  |

|         | 2.2.1 | Memory Configuration              | 2-4  |

|         | 2.2.2 | Static Column Modes               | 2-4  |

|         | 2.2.3 | Page Mode/Static Column Detection | 2-5  |

|         | 2.3   | COM20020                          | 2-5  |

|         | 2.4   | DMAC                              | 2-6  |

|         | 2.4.1 | DMA and SCSI Control              | 2-6  |

|         | 2.4.2 | Coprocessor Interface             | 2-9  |

|         | 2.4.3 | SSPB Control                      | 2-10 |

| CHAPTER | 3     | The Pandora Chips                 |      |

|         | 3.1   | Basic Description                 | 3-1  |

|         | 3.2   | New Features                      |      |

|         | 3.2.1 | Bitplanes                         | 3-3  |

|         | 3.2.2 | Sprites                           |      |

|         | 3.2.3 | Video                             | 3-4  |

|         | 3.2.4                                                                                                     | Compatibility                                                                                                                                                                                                                               | 3-5                                                                |

|---------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|         | 3.2.5                                                                                                     | Genlock Stuff                                                                                                                                                                                                                               | 3-5                                                                |

|         | 3.2.6                                                                                                     | Color Lookup Table                                                                                                                                                                                                                          | 3-5                                                                |

|         | 3.2.7                                                                                                     | Collision                                                                                                                                                                                                                                   | 3-6                                                                |

|         | 3.2.8                                                                                                     | Horizontal Comparators                                                                                                                                                                                                                      | 3-6                                                                |

|         | 3.2.9                                                                                                     | Mouse/Joysticks                                                                                                                                                                                                                             | 3-6                                                                |

|         | 3.2.10                                                                                                    | Coersion of 15kHz to 31kHz                                                                                                                                                                                                                  | 3-6                                                                |

| CHAPTER | 4                                                                                                         | The DSP3210 Subsystem                                                                                                                                                                                                                       |                                                                    |

|         | 4.1                                                                                                       | WE® DSP3210 Overview                                                                                                                                                                                                                        | 4-1                                                                |

|         | 4.2                                                                                                       | DSP System Configuration                                                                                                                                                                                                                    | 4-2                                                                |

|         | 4.2.1                                                                                                     | DSP Memory Map Differences                                                                                                                                                                                                                  |                                                                    |

|         | 4.2.2                                                                                                     | The DSP Reset Mechanism                                                                                                                                                                                                                     |                                                                    |

|         | 4.2.3                                                                                                     | The BIO Port                                                                                                                                                                                                                                | 4-4                                                                |

|         | 4.3                                                                                                       | DSP Serial I/O                                                                                                                                                                                                                              | 4-4                                                                |

|         | 4.3.1                                                                                                     | The Phone-Line CODEC                                                                                                                                                                                                                        | 4-5                                                                |

|         | 4.3.2                                                                                                     | The Hi-Fi Audio CODEC                                                                                                                                                                                                                       | 4-7                                                                |

|         | 4.4                                                                                                       | Other DSP Information                                                                                                                                                                                                                       | 4-7                                                                |

|         |                                                                                                           |                                                                                                                                                                                                                                             |                                                                    |

| CHAPTER |                                                                                                           | System Expansion                                                                                                                                                                                                                            |                                                                    |

| CHAPTER |                                                                                                           |                                                                                                                                                                                                                                             |                                                                    |

| Chapter | 5                                                                                                         | System Expansion                                                                                                                                                                                                                            | 5-1                                                                |

| Chapter | 5<br>5.1                                                                                                  | SYSTEM EXPANSION<br>The Local Bus Slot                                                                                                                                                                                                      | 5-1<br>5-2                                                         |

| Chapter | 5<br>5.1<br>5.2                                                                                           | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus                                                                                                                                                                                 | 5-1<br>5-2<br>5-2                                                  |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3                                                                             | SYSTEM EXPANSION<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot                                                                                                                                                               | 5-1<br>5-2<br>5-2<br>5-2                                           |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1                                                                    | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections                                                                                                                                          | 5-1<br>5-2<br>5-2<br>5-2<br>5-3                                    |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2                                                           | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals                                                                                                                         | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-4                             |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3                                                  | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals                                                                                                        | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-4                             |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4                                         | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals<br>Audio Signals                                                                                       | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-4<br>5-5                      |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5                                | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals<br>Audio Signals<br>Port Connections                                                                   | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-4<br>5-5<br>5-5               |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.4                         | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals<br>Audio Signals<br>Port Connections.<br>The CD/AUX Connector                                          | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-4<br>5-5<br>5-5<br>5-6<br>5-6 |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.4<br>5.5                  | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals<br>Audio Signals<br>Port Connections<br>The CD/AUX Connector<br>The DSP Connector                      | 5-1<br>5-2<br>5-2<br>5-3<br>5-4<br>5-5<br>5-5<br>5-6<br>5-6<br>5-6 |

| Chapter | <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.4<br>5.5<br><b>5</b> .5.1 | System Expansion<br>The Local Bus Slot<br>The Zorro III Bus<br>The Video Slot<br>Power Connections<br>Clock Signals<br>Video Signals<br>Audio Signals<br>Port Connections<br>The CD/AUX Connector<br>The DSP Connector<br>Power Connections | 5-1<br>5-2<br>5-2<br>5-3<br>5-4<br>5-5<br>5-5<br>5-6<br>5-6<br>5-6 |

| A.1   | External Connector Pinouts |     |

|-------|----------------------------|-----|

| A.1.2 | Mouse Port                 |     |

| A.1.2 | Keyboard Port              | A-2 |

| A.1.3 | Serial Port                |     |

| A.1.4 | Parallel Port              |     |

| A.1.5 | Floppy Port                |     |

| A.1.6 | SCSI Port                  | A-2 |

| A.1.7 | Audio Port                 | A-3 |

| A.1.8 | Video Port                                      | A-3  |

|-------|-------------------------------------------------|------|

| A.2   | Internal Connector Pinouts                      | A-4  |

| A.2.1 | Power Connector                                 | A-4  |

| A.2.2 | CD/AUX Connector                                | A-4  |

| A.2.3 | DSP Connector                                   | A-4  |

| A.2.4 | Floppy Connector                                | A-4  |

| A.2.5 | SCSI Connector                                  | A-5  |

| A.2.6 | Daughterboard Slot                              | A-5  |

| A.2.7 | Video Slot                                      | A-6  |

| A.2.8 | Zorro III Slot                                  | A-7  |

| A.2.9 | Local Bus/Coprocessor Slot                      | A-8  |

| A.3   | System Configuration Jumpers                    | A-11 |

| A.4   | I <sup>2</sup> C Bus Information                | A-13 |

| A.4.1 | Configuring SSPB for I <sup>2</sup> C protocols | A-13 |

| A.4.2 | A3000+ Audio Processor                          | A-14 |

| A.4.3 | A3000+ RAM/Clock                                | A-15 |

| A.5   | Additional Pandora Information                  | A-18 |

| A.5.1 | Common Pandora Display Modes                    | A-18 |

| A.5.2 | Pandora Register Summary                        | A-18 |

| A.6   | Additional CODEC Information                    | A-25 |

| A.6.1 | The Phone-Line CODEC                            | A-25 |

| A.6.2 | The Hi-Fi Audio CODEC                           | A-27 |

| A.7   | References                                      | A-31 |

# TABLES AND FIGURES

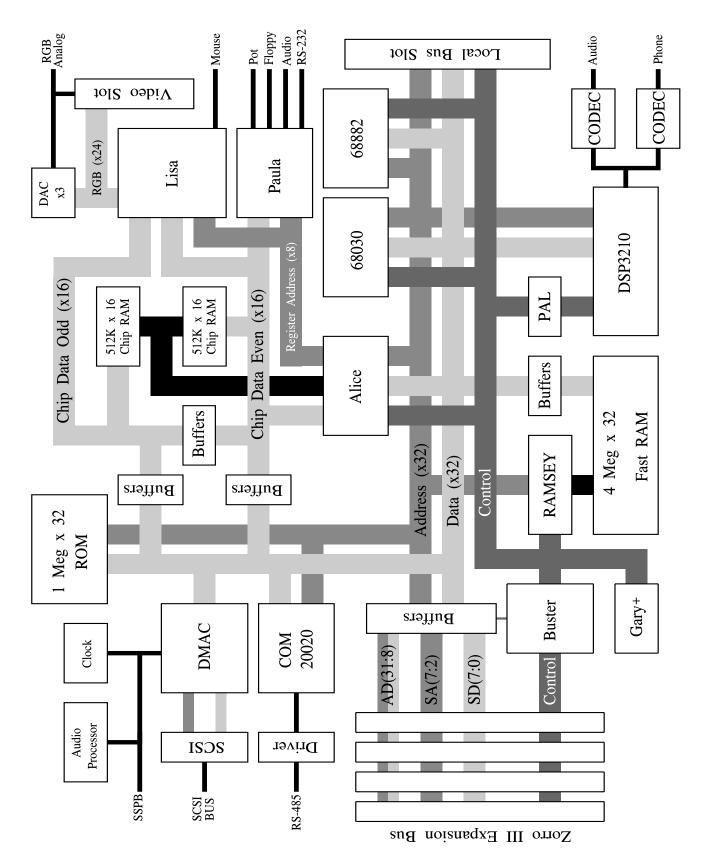

| Figure | 1-1 | Amiga 3000+ System Structure        | 1-3  |

|--------|-----|-------------------------------------|------|

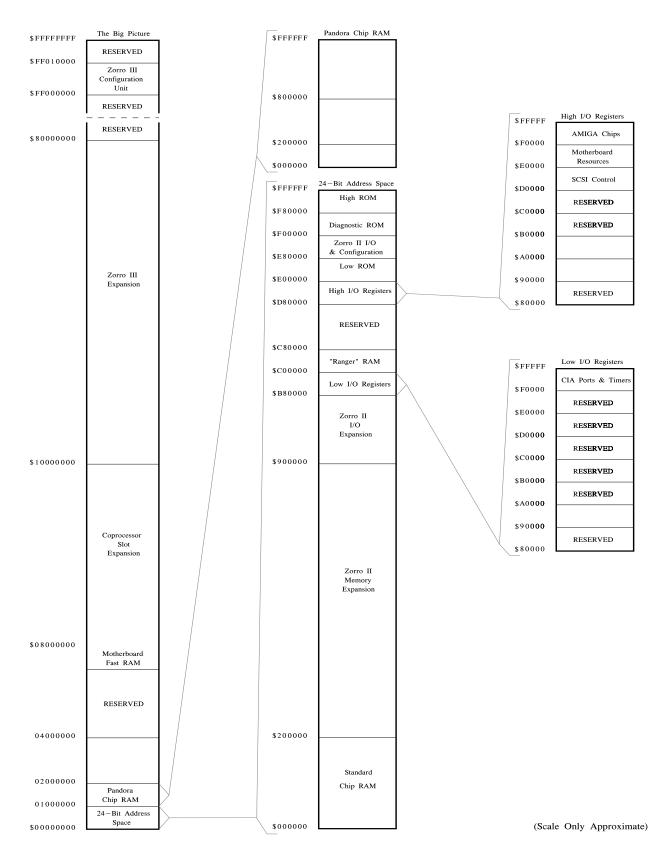

| Figure | 1-2 | Amiga 3000+ Memory Map              | 1-4  |

| Table  | 2-1 | Gary+ Registers                     | 2-2  |

|        |     | RAMSEY Registers                    |      |

| Table  | 2-3 | Refresh Timing                      | 2-4  |

| Table  | 2-4 | COM20020 Registers                  | 2-6  |

| Table  | 2-5 | DMAC/SCSI Registers                 | 2-7  |

| Table  | 2-6 | Control/Interrupt Bit Assignments   | 2-8  |

| Table  | 2-7 | Coprocessor Control Bit Assignments | 2-9  |

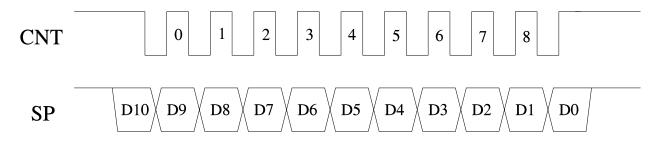

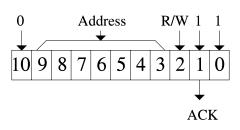

| Figure | 2-1 | SSPB Clock/Data Format              | 2-11 |

| Table  | 3-1 | Pandora HAM Encodings               | 3-3  |

| Table  | 3-2 | Lisa Color Mapping                  | 3-5  |

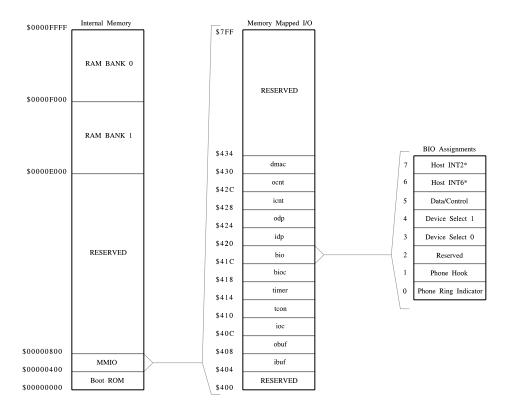

| Figure | 4-1 | DSP3210 Internal Memory Map         | 4-3  |

| Table  | 4-1 | The DSP3210 ioc Register            | 4-5  |

| Table  | 4-2 | Phone-Line CODEC Registers          | 4-6  |

# CHAPTER 1

### INTRODUCTION

Thou shalt not bring into the world knowledge and devices that will harm mankind. -Herbert A. Simon

The Amiga 3000+ computer is a second generation Amiga 3000 class computer. It shares many of the Amiga 3000 system's features, while adding a significant number of enhancements, designed to increase the Amiga line's support of more advanced video and audio playback and processing. It is intended to be upward compatible with the Amiga 3000, and shares most mechanical specifications with the Amiga 3000 as well.

This document is intended to collect, in one single place, all of the hardware details of the Amiga 3000+. Obviously, it won't reach this goal completely. There is far too much information pertinent to the A3000+ to reproduce in a single document. Therefore, where appropriate, additional documents are referenced, leaving the bulk of the space available for material specific to the A3000+. This document should be all that's necessary, for example, to port a new operating system to the A3000+, assuming one obtains other generic materials, such as the microprocessor and expansion bus specifications. It also collects all A3000+ connector pinouts and I/O register definitions in a single place, though both of these items may be better described in other documents.

#### **1.1 Basic Description**

The Amiga 3000+ takes the best features of the Amiga 3000, like 32-bit architecture, video compatibility, expandability, and adds new features to better suit current and future graphics,

sound, and video applications. The complete feature list is, in essence, this document. The basic highlights, though, are as follows:

- 25MHz MC68030/MC68882 Main Processor

- 50MHz ATT DSP3210 Coprocessor

- Amiga "Pandora" graphics chip set

- Improved 32-bit DRAM and SCSI DMA controllers

- Enhanced video expansion slot

- New audio I/O ports

- Support for 4MB ROM

- Built-in telephone line interface

- Built-in 2.5 Mbit/second RS-485 network port

The basic system architecture is shown in *Figure 1-1*. The organization of the A3000+ hardware is very similar to that of the A3000. The central processor is a Motorola 68030 clocked at 25MHz, with 68882 floating point coprocessor also at 25MHz. The main motherboard controller is the Gary+ chip, a custom gate array. This generates chips selects for and timing for motherboard slave resources other than Fast RAM. On the A3000+, these resources include the Amiga "Pandora" chip set (Alice, Lisa, Kelly, and Paula), up to 4MB of ROM, two 8520 Complex Interface Adaptor chips, a Standard Microsystems COM20020 network interface chip, and a custom Amiga DMA controller for SCSI bus. On the A3000+, the DMAC also contains registers for coprocessor control and the SSPB interface, a Synchronous Serial Peripheral Bus used for battery backed RAM/Clock, Audio processor, and Video Slot expansion.

To additional motherboard resources manage their own control functions. The RAMSEY chip controls up to 16MB of memory on the motherboard, with facility for burst and page-detection modes when used with static column DRAM. The RAMSEY device also acts as an address generator for the DMAC during SCSI DMA transfers. The Buster chip controls the standard Amiga expansion bus, suppoting both Zorro II and Zorro III procotols. It manages bus arbitration for both expansion, motherboard, and coprocessor slot resources.

In addition to the 68030 system, the Amiga 3000+ has an on-board DSP coprocessor, the ATT DSP3210 clocked at 50MHz. This processor has direct memory access to all 32 bit motherboard resources, just as the 68030. In addition, it has a private high speed serial bus with DMA access to 3210 internal memory. The A3000+ provides two serial bus devices, a telephone line interface CODEC and a 16 bit stereo audio CODEC. The DSP expansion connector provides two additional channels on the serial bus, to support the additional DSP peripherals.

#### **1.2 Memory Organization**

All Amigs 3000+ memory and I/O resources are memory mapped. The A3000+ memory map is illustrated in *Figure 1-2*. This is a superset of the A3000 memory map, with allocations for the new A3000+ resources and definitions for various extensions to this basic memory map to handle possible future enhancements

There are a few memory aliases present in this map, to support backward compatibility with the

Figure 1-1: Amiga 3000+ System Structure

The A3000+ System Specification

Figure 1-2: Amiga 3000+ Memory Map

A3000 and earlier systems. Chip RAM, for example, is mapped as in earlier systems at \$00000000-\$001FFFFF. Since the orginal Amiga architecture supported only 2MB of Chip RAM, though, any additional Chip memory will have to be mapped non-contiguously. The A3000+ solution to this is to map the memory at \$00000000 to the base of a new region, starting at \$01000000. The A3000+ architecture physically supports 8MB of Chip RAM, so should an 8MB Alice be designed, the additional 6MB winds up in the \$01200000-\$017FFFFF range. The next 8MB has been reserved for use as Chip RAM in future systems.

Similarly, the A3000 used up all the reserved ROM space in the original Amiga memory map, the range from \$00F80000-\$00FFFFFF, for the 512K space used by AmigaOS 2.0. To support at least 1MB of ROM on machines with 24 bit addressing, the previously unused 512K from \$00E00000-\$00EFFFFF. To support additional ROM in an upward compatible fashion, the A3000+ addresses 4MB of ROM at \$03C00000-\$03FFFFFF. The 512K chunk at \$00F80000 is also mapped at \$03F80000.

Some details of the A3000+ memory organization are too small to show up on this chart. The Gary+ has a number of important control registers, which are described in the next chapter. The DMAC, along with its normal DMA controller functions, also has the Coprocessor Control and SSPB registers mapped in its space. These are also covered in the next chapter. While not shown in the memory map, the DSP3210 has some internal resources that overlay the A3000+ memory as mapped by the 68030. These will be covered in the DSP3210 chapter.

Chapter 1: Introduction

# CHAPTER 2

## MAIN SYSTEM CONTROLS

We're definitely coming to the post-IBM era.

-Joel Tessler

There are lots of function in the Amiga 3000+, and not surprisingly, lots of control registers associated with these features. Theese control registers are physically located in the various system chips.

#### 2.1 Gary+

The Gary+ chip is essentially the motherboard controller in the Amiga 3000+. It performs the following functions:

- Chip select and sometimes timing for Alice, the two 8520s, the DMAC, the ROM, the 68882, the COM20020, and the Local Bus Slot select.

- Chip RAM buffer and CPU byte access control.

- Genlock/internal clock multiplexing

- Reset control, including powerup detect, keyboard reset with disable, and DSP reset.

- Fast interrupt disable control.

- Bus timeout and error control.

- High order address generation for Zorro II DMA.

The chip selects should be pretty self-explanatory. The Gary+ design insures that each chips gets the length and bus size it requires. The ROM cycle is programmable via a PCB jumper to either

160ns or 280ns. Access to Chip RAM is done, as in other Amiga system, according to what the Chip RAM controller, Alice in this case, is doing. It is still possible to set up bandwidth intensive display and blitter functions with Alice, so the Chip RAM access is alway potentially variable.

Gary+ has a number of programmable control registers. These registers are located on byte boundaries, in Supervisor data space, and each contains one significant bit, which will be D7 in the access byte. The registers are shown in *Table 2-1*.

| Register   | Bit | Name             | Function               |

|------------|-----|------------------|------------------------|

| -          |     |                  |                        |

| \$00DE0000 | 7   | TIMEOUT          | Controls bus timeout   |

| \$00DE0001 | 7   | TOENB*           | Time out enable        |

| \$00DE0002 | 7   | COLDSTART        | Indicates cold powerup |

| \$00DE1000 | 7   | DSPRST*          | DSP reset line         |

| \$00DE1001 | 7   | KBRSTEN          | Keyboard reset control |

| \$00DE1002 | 7   | GARYID           | Serial ID code         |

|            |     | Table 2-1: Gary+ | Registers              |

#### **2.1.1 Bus Timeout Support**

The Gary+ timeout support is necessary to trap processor access to unmapped memory resources. In early Amigas, the motherboard controller would simply run zero wait state cycles for all memory accesses unless instruction to add waits for Chip bus or expansion resources. This policy has two problems. First of all, it makes detecting access to non-existant memory very difficult. Secondly, it pretty much requires one central agency to do all of the cycle timing in the system. Being a more sophisticated Amiga system, the A3000+ really needs the ability to trap random addressing in hardware. And cycle termination isn't central; it comes from several different places, such as Gary+ itself, RAMSEY, Buster, the 68882, and a possible slave device in the Local bus slot.

At power up, the TIMEOUT and TOENB\* registers are both zero, which indicates that the default timeout is selected. Default timeout yields an automatic 32 bit asynchronous cycle termination (via /DSACK<sub>0</sub> and /DSACK<sub>1</sub>) after  $9\mu$ S, effectively ignoring the access. This mode is used during power up, since the OS polls certain memory locations that may not respond, and we don't want powerup to take all day. When a one is written to TIMEOUT, the detectable timeout mode is set. This causes a termination via /BERR after 250 mS. This is the normal operating mode of A3000 class systems under AmigaOS 2.0. For special purposes, timeout may be turned off altogether. This is done by writing a one to the TOENB\* register. Also, since the Chip bus may lock the CPU out for extended periods of time, all timeout logic is disabled during an access to any Chip bus resource.

#### 2.1.2 Reset Control

Gary+ has several registers associated with system reset. The COLDSTART register detets a power up condition, so that software can distinguish cold boots from warm boots. This register will be set high on power up only; once written low, it will stay low until the next power cycle. The DSPRST\* line goes low on reset and stays low until a one is written to it. This allows the 68030 to get things in order before turning on the DSP3210. The KBRSTEN bit powers up low, which allows keyboard resets to generate system reset just like in any other Amiga system. If this bit is set high, however, the keyboard reset will be ignored.

#### 2.1.3 Gary+ ID

The GARYID register is used to get the 8 bit Gary+ ID, which identifys the type of Gary and the revision level of that type. To initiate the ID code stream, a zero is written to GARYID. The bits of the Gary ID code are then read from GARY+ in eight reads of the GARYID register. The code is extracted MSB first. The first four bits of the code indicate the type of system controller, the last four bits indicate the revision level. This register is constructed in such a way that this same technique works on the Amiga 3000. The A3000's Gary returns the code \$00, the Gary+ returns the code \$90.

| Register   | Bit | Name                | Function                 |

|------------|-----|---------------------|--------------------------|

| \$00DE0003 | 7   | TEST                | Used for production test |

|            | 6,5 | <b>REFRESH RATE</b> | Timing for refresh       |

|            | 4   | RAMWIDTH            | Set up for x4 or x1 RAM  |

|            | 3   | RAMSIZE             | 1MB or 4MB density       |

|            | 2   | WRAP                | Enable burst wrapping    |

|            | 1   | BURST               | Run 68030 burst cycles   |

|            | 0   | PAGE DETECT         | Use page-detect logic    |

| \$00DE0043 | 7-0 | VERSION             | RAMSEY chip version      |

|            |     | Table 2-2:RAMSEY F  | Registers                |

#### 2.2 RAMSEY

The A3000+ RAM controller is an improved version of the A3000 RAMSEY chip. The RAMSEY chip directly manages 16MB of 32 bit wide Fast RAM. A number of the RAMSEY features can be tuned, depending on the memory connected. The RAMSEY registers, all 8-bit registers located in Supervisor Data space, are show in *Table 2-2*. Writes to \$00DE0003 don't actually take effect until the next refresh cycle. A read loop on the changed bit can be used if it necessary to wait for a change. RAMSEY controlled Fast RAM is located from \$07FFFFFF building down toward \$00700000, as far as the populated memory will take it.

#### 2.2.1 Memory Configuration

The preferred A3000+ configuration is with static column DRAM in the 256Kx4 or 1MBx4 packages. RAMWIDTH defaults to one, which sets RAMSEY up for operation properly as far as the A3000+ is concerned. With RAMWIDTH set to zero, RAMSEY will drive 1MBx1 DRAM, though the A3000+ motherboard can't physically accomodate these parts. RAMSIZE is set by J852 on the A3000+ motherboard, it reads low for 256Kx4, high for 1MBx4. The RAMSIZE register can be written to, though there's generally no need for that.

DRAM Refresh is programmed by the REFRESH RATE bits, according to the timing shown in *Table 2-3*. The refresh time may have to be adjusted for the memory mode in effect. In basic access mode, the DRAM need one refresh cycle every  $15.625\mu$ S or more. However, during a static column cycle resulting from page-detect mode, the DRAM need a refresh cycle every 10  $\mu$ S or more. Any program modifying the OS or powerup settings of these bits needs to take this into acount.

| 00 | 154 | 6.16       |

|----|-----|------------|

| 01 | 238 | 9.52       |

| 10 | 380 | 15.2       |

| 11 | N/A | No Refresh |

#### 2.2.2 Static Column Modes

On powerup, RAMSEY runs a five clock cycle to DRAM. This cycle will work with either page mode or static column DRAM rated for 80ns operation. There are two enhanced modes that take advantage of static column memory to speed things up. The first of these is the burst mode, which is set by setting the BURST bit high. This causes RAMSEY to assert /CBREQ when accessed and run a 68030 style burst cycle when /CBACK is asserted by the current bus master. Burst cycles take two clocks each. The burst cycle operation is modified by the WRAP bit. The 68030 burst cycle always starts on a longword that the 68030 wants, and in the process gets the other three in the natural quadlongword defined by the first access. This means that burst wraps around behind the first longword when that longword isn't first in the quadlongword. With BURST set to one, natural 68030 burst takes place. With BURST set to zero, the burst cycle won't wrap backwards, but instead terminate with less than four longwords fetched. Note that the 68040 doesn't support aborted bursts, so WRAP much be one for most 68040 systems.

The other enhanced RAMSEY mode is called page-detect mode. When RAM is first accessed, RAS is held low after the cycle completes. This leaves the current RAM page "open", and the RAM bank will act like static RAM while accesses continue on this page. While accesses continue on-page, access time is driven by column rather than the longer row access time. Memory cycles complete in three clocks while on-page. Comparators in RAMSEY monitor the

new row addresses for every new cycle until a refresh comes along, which can be for up to  $10\mu$ S The downside of this mechanism is that, when the page detector finds a page miss, the currently open page must be closed properly before a new one can be opened. This takes seven clocks, two to close the page, five to normally open the new one. This mode tends to work very well when memory accesses tend to be linear. It helps considerably during access by the DMAC or DSP3210, both of which have very linear access patterns. Under normal 68030 and AmigaOS use, this mode is sometimes a win, sometimes a loss.

Note that, due to a chip bug, original A3000 versions of RAMSEY (version code \$0D) don't correctly support this mode. The A3000+ RAMSEY supports this mode properly. Any program messing with RAMSEY control registers should check for a version \$0E or later RAMSEY before enabling this feature.

#### 2.2.3 Page Mode/Static Column Detection

RAMSEY was originally designed to use static column memory exclusively. Because of these, there's no explicit support of page mode DRAM, though of course, page mode memory will work as long as no special features are enabled. The trick is detecting that page mode memory is in the A3000+ in the first place. The method for checking is as follows:

- 1) Disable all interrupts

- 2) Turn page detect mode on via the PAGE bit (be sure to wait until it takes effect).

- 3) Write \$5AC35AC3, \$AC35AC35, \$C35AC35A, \$35AC35AC to four consecutive longwords in a quadlongword.

- 4) Turn page detect mode off via the PAGE bit (again, wait for it to take effect).

- 5) Compare what's now in the selected quadlongword with what was written. If the data is correct, that bank has all static column DRAM in it.

- 6) Repeat steps 2 through 5 for each bank of memory.

- 7) Re-enable interrupts. If any bank contains page mode DRAM, none of the static column features can be used.

#### 2.3 COM20020

The COM20020 Universal Local Area Network Controller is the engine behind the low cost RS-485 network in the A3000+. This device implements the physical layer of a 2.5 Mbps deterministic, token passing network interface. The device has 2K of on-chip dual port RAM for buffering of packets in both directions

The A3000+ configures the COM20020 in a bussed network configuration, based on the RS-485 twisted pair bus standard. The A3000+ uses RCA-type phono jacks for the physical connection. The connector is self-terminating; when a jack is plugged in, the terminator is removed from the bus. In this way, it's guaranteed that termination is placed at the end of the bus, and only at the end of the bus.

The COM20020 is fully described in the document <u>COM20020 Universal Local Area Network</u> <u>Controller (ULANC)</u>, from Standard Microsystem Corporation, Component Products Division. The part is mapped in the A3000 system as a 32 bit device, located at \$00D90000. Since the device has an eight bit data bus, each COM20020 register occupies only the first eight bits of each consecutive longword based location. The basic register map is given in *Table 2-4*.

| Address    | Read Function        | Write Function       |

|------------|----------------------|----------------------|

| \$00D90000 | Status               | Interrupt Mask       |

| \$00D90004 | Diagnostic Status    | Command              |

| \$00D90008 | Address Pointer High | Address Pointer High |

| \$00D9000C | Address Pointer Low  | Address Pointer Low  |

| \$00D90010 | Data                 | Data                 |

| \$00D90014 | Reserved             | Reserved             |

| \$00D90018 | Configuration        | Configuration        |

| \$00D9001C | TentID/NodeID/Setup  | TentID/NodeID/Setup  |

#### **2.4 DMAC**

The DMAC is an improved version of the A3000 DMAC. This chip's main function is to act as a data transfer unit to the Western Digital 33C93 SCSI controller. The A3000+ version of this part has a FIFO increased to eight longwords deep, and it can now run as fast as the 68030 to 32 bit memory. It can also handle word-aligned DMA transfers, where the earlier device required longword aligned buffers. The new DMAC is designed to be compatible with the A3000 and A3000 software, so some bit assignments and features may seem strange.

Due to pin count restrictions, most DMAC control registers are not mapped strictly according to 68030 bus rules. All DMAC registers are accessed as longword-wide registers. However, they will always behave as whole longwords, even if accessed via word or byte instructions; it is impossible to independently access individual words or bytes within these registers. Therefore, any writes to DMAC registers must write all significant bits, and any reads from DMAC registers will appear to read the entire register, even if the machine op-code would claim otherwise.

#### 2.4.1 DMA and SCSI Control

The DMAC and WD 33C93 SCSI controller chips work together as a team for most kinds of SCSI transfers. The WD 33C93 registers are actually mapped into the DMAC register space, as shown in *Figure 2-5*. Registers labelled "Read" are read-only registers, and "Write" are write-only. Those labelled "R/W" can be read or writtern. "Strobe" registers will cause a

specific action to take place when read or written, regardless of the data value involved. The WD3393 registers are mapped a little strangely. There are two WD33C93 registers, each of which is a byte-wide register. These were mapped in the A3000 based on 68030 behavior, rather than 68030 specificatios, so properly designed 68040 cards could not access these registers as bytes. Allowing access to SASR\_L solved this for the 68040, but due to a cache bug in the 68030, this caused a problem correctable only with the MMU. The mapping in the enhanced DMAC provides byte-wide mapping that works for 68030 or 68040.

| Register   | Name    | Туре   | Function                  |

|------------|---------|--------|---------------------------|

| \$00DD0004 | WTC     | R/W    | Word Transfer Count (obs) |

| \$00DD0008 | CONTR   | R/W    | Control Register          |

| \$00DD000C | ACR     | R/W    | Address Control Register  |

| \$00DD0010 | ST_DMA  | Strobe | Start DMA                 |

| \$00DD0014 | FLUSH   | Strobe | Flush FIFO                |

| \$00DD0018 | CLR_INT | Strobe | Clear Interrupts          |

| \$00DD001C | ISTR    | Read   | Interrupt Status Register |

| \$00DD003C | SP_DMA  | Strobe | Stop DMA                  |

| \$00DD0040 | SASR_L  | Write  | WD33C93 SASR long (obs)   |

| \$00DD0041 | SASR_B  | Read   | WD33C93 SASR byte (obs)   |

| \$00DD0047 | SCMD_B  | R/W    | WD33C93 SCMD byte         |

| \$00DD0049 | SASR_B  | R/W    | WD33C93 SASR byte         |

The WTC register is considered obselete, and is not actually supported in the A3000+ DMAC. It can be used to determine if new or old style DMAC is in a system, however. Bit two of the register is fixed at zero in the new part, but is a read/write bit in the old part. So writing a longword with bit two set, then reading it back, will determine which part is installed in a system. All A3000+ systems will have the new part, though A3000 systems may have either.

The DMAC control register, CONTR, contains four significant bits in a 32-bit word, as shown in *Table 2-6*. The DMAENA bit, reads high end DMA is enabled, low when DMA is disabled. Reset or the SP\_DMA strobe cause this to go low, while the ST\_DMA strobe causes it to go high. The PREST bit will reset the WD33C93 if a high is written to it, while low lets the WD33C93 operate normally. The INTENA enables the generation of a system interrupt by the DMA controller. Finally, the DMADIR bit indicates the direction of data transfer for a DMA operation. A high written here causes a data transfer from Amiga memory to the SCSI bus, while a low here causes data transfer to go from the SCSI bus to Amiga memory.

The ACR indicates the starting byte in the 32 bit address space for a DMA transfer. Note that the ACR, physically contained in the RAMSEY chip, will actually round any value written to it down to an even word, since the DMAC doesn't support odd-byte aligned transfers. This

register must be updated for every new DMA transfer. Note that the length of the transfer can actually be an odd number of bytes, as explained in the discussion of the FLUSH strobe.

The ST\_DMA strobe starts the DMA transfer. Once the ACR and CONTR registers are properly set for a transfer, a read or write of this strobe causes the transfer to take place. The ACR must be reset for every new DMA transfer. The SP\_DMA strobe causes the current DMA to unconditionally abort, and all internal DMA related registers to be reset. This location must be strobed prior to setting up a new DMA transfer. The FLUSH strobe causes the FIFO to be flushed in the case of a transfer from SCSI to main memory. This location must be strobed after the WD33C93 indicates the end of SCSI activity. If the last element of the FIFO contains one or two bytes, a word is written; if three or four bytes, a longword is written. A strobe of flush causes immediate DMA activity; the FIFO will be flushed on the instruction following the strobe, from the CPU's point of view.

| Register | Bit | Name   | Function          |

|----------|-----|--------|-------------------|

| CONTR    | 8   | DMAENA | DMA enabled       |

|          | 4   | PREST  | WD33C93 reset     |

|          | 2   | INTENA | Interrupt enable  |

|          | 1   | DMADIR | DMA direction     |

| ISTR     | 7   | INT_F  | Interrupt follow  |

|          | 6   | INT_S  | Interrupt SCSI    |

|          | 5   | E_INT  | End of process    |

|          | 4   | INT_P  | Interrupt pending |

|          | 1   | FF     | FIFO Full         |

|          | 0   | FE     | FIFO Empty        |

The CLR\_INT strobe clears all interrupts registered by ISTR, and negates the DMAC's interrupt output line. The ISTR register is responsible for recording interrupts, as shown in *Table 2-6*. Bits INT\_F, INT\_S, and E\_INT each reflect the status of the WD33C93 interrupt line, which is an active high interrupt. The INT\_P bit is low if INTENA is cleared, otherwise it indicates the status of the WD33C93 line, and will of course also indicate that an interrupt has actually be sent to the system by the DMAC. The FF bit goes high when the FIFO is full, and the FE bit goes high when the FIFO contains less than one longword.

The SASR and SCMD registers are part of the WD33C93 specification. They are fully described in the Western Digital publications "WD33C93A SCSI Bus Interface Controller" for the WD33C93A, and "WD33C93B (SBIC) Enhanced SCSI Bus Interface Controller" for the WD33C93B. The current intent is to use the latter part in the A3000+, though that depends on availability from Western Digital.

#### 2.4.2 Coprocessor Interface

The coprocessor interface register is located at \$00DD0050, with data direction register at \$00DD0054. This register is used for signalling between the 68030, the DSP3210, and optionally, a Local Bus Slot device. The A3000+ system assignments for this port are given in *Table 2-7*. The 32-bit register contains eight significant bits, all of which are reset to inputs (DDR is set to \$xxxxxFF) on reset. Bits seven and six are currently unassigned.

The bit assignments start with the five and four, which are for coprocessor slot communications. The CI2P\* bit is earmarked as an input from the coprocessor slot. The PI2C\* bit is earmarked as an output to the coprocessor slot. These bits have no pre-defined definition, but instead are for the use of the private signalling protocol that may be desired between a coprocessor slot device and the main system.

| Bit | Name      | DDR      | Function                            |

|-----|-----------|----------|-------------------------------------|

|     |           |          |                                     |

| 7,6 | N/A       | Ι        | Reserved                            |

| 5   | CI2P*     | Ι        | Coprocessor signal to processor     |

| 4   | PI2C*     | 0        | Processor signal to coprocessor     |

| 3   | INT6*     | Ι        | DSP caused level 6 system interrupt |

| 2   | INT2*     | Ι        | DSP caused level 2 system interrupt |

| 1   | DSP1*     | 0        | Cause DSP level 1 interrupt         |

| 0   | DSP0*     | 0        | Cause DSP level 0 interrupt         |

| -   | _ ~ ~ ~ ~ | -        |                                     |

|     | Table 2-7 | 7: Copro | cessor Control Bit Assignments      |

The rest of the coprocessor interface register is concerned with the motherboard's DSP3210 coprocessor. The DSP3210 can generate level 6 or level 2 interrupts, in the traditional Amiga shared interrupt protocol. INT6\* and INT2\* should be read, respectively, by DSP interrupt handlers to determine if the DSP was in fact the device pulling either interrupt. The DSP3210 will actually turn off the interrupt it's pulling as part of the DSP to host CPU software interface protocol. The host CPU can in turn generate DSP interrupts by writing lows to either DSP1\* or DSP0\*. Again, software protocols are necessary to ensure that the host CPU negates either interrupt line at the appropriate time. More information on DSP and host interaction is contained in the DSP3210 chapter.

In normal use, this register should be initialized to \$FF before changing any of the data direction control bits to outputs. Failure to do this may cause unhandled interrupts to either host or DSP processors. It may also cause undefined behavior in Coprocessor slot boards that take advantage of the CI2P\* and PI2C\* lines. An I/O reset will reset the data direction register to all inputs, but has no effect on the stored output values.

#### 2.4.3 SSPB Control

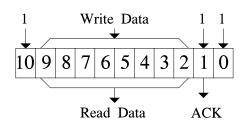

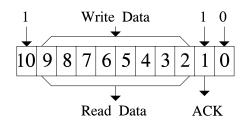

The Synchronous Serial Peripheral Bus (SSPB) interface consists of a data register at \$00DD0058 and a control register at \$00DD005C. The SSPB bus is a flexible two-wire interface for control of low speed peripherals. It consists of a data line, SP, and a clock line, CNT. The SSPB control registers allow virtually any possible two-wire synchronous serial bus to be implemented under CPU control, but they provide automatic clocking with interrupt-when-done for serial protocols than can be constructed from eleven bits or less of data.

Before any SSPB activity can take place, the SSPB control register (SSPBCTL) must be set up. The bit assignments of the SSPB Control Register is given in *Table 2-8*. The XDONE bit goes high to indicate that a successful transfer has completed; it is cleared on read, a no-op on write. The INTENB bit is written low to disable interrupts, high to cause an interrupt to be generated by the DMAC when a byte has been transferred over the SSPB bus. Interrupts are generally used by all clocked SSPB protocols.

| Bit                       | Name                                                           | Function                                                                                                 |

|---------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 11<br>10<br>9<br>8<br>7-0 | XDONE<br>INTENB<br>ACNT*<br>ASP*<br>COUNT<br>Table 2-6: SSPB ( | Transfer complete<br>Interrupt enable<br>Raw access to CNT line<br>Raw access to SP line<br>CNT timebase |

A high written to ACNT\* will cause a low on the CNT line when the SSPB mechanism is not in a clocked transfer, and a high written to ASP\* will cause a low on the SP line when the SSPB mechanism is not in a clocked transfer. ACNT\* and ASP\* read, respectively, the current state of the CNT and SP lines. This allows the an active programming of the CNT and SP lines, to create serial protocols not supported by the clocked SSPB protocol.

The SSPB automatic clock period is determined by the value written to the CLOCK byte. The cycle time of CNT is given by (CLOCK \* 160ns), for values of CLOCK from 1 to 255. The value of CLOCK is preserved over multiple SSPB data cycles.

Once SSPBCTL has been set up, SSPB data transfer cycles may be run. The SSPB data cycle is a little unusual, in that every cycle is technically both a read and write cycle. To start an SSPB cycle, the host processor writes to the 32 bit wide SSPB data register (SSPBDAT) a data value with the lower eleven bits significant. The SSPB mechanism then proceeds to shift out this data, from bit eleven through bit zero. Bit eleven is shifted out before the first clock on CNT, and bit zero is shifted out after the last clock on CNT, as shown in *Figure 2-1*. Once the transfer is complete, the DMAC will bring the system interrupt line low, assuming the INTENB bit is set,

and the host CPU will receive an interrupt, which is held until cleared by reading SSPBCTL. Once the interrupt is cleared, SSPBDAT may be read.

This event sequence holds for either reads from or writes to SSPB devices. For a write, the write data is simply written to SSPBDAT, possibly mixed in with control information, depending on the data format in use. When called in an interrupt server chain, the SSPB server reads SSPBCTL, checking for XDONE. If asserted, SSPBDAT may optionally be checked for any sort of status the protocol in use would demand. For a read, each significant data bit is set high in a write to SSPBDAT. Upon receipt of an interrupt, the interrupt server gets the XDONE bit from SSPBCTL and then the read data and possible status from SSPBDAT.

Figure 2-1: SSPB Clock/Data Format

The actual SSPB protocol used depends on what the interface is used for. At present, the A3000+ has two SSPB devices on the motherboard, the battery backed clock/RAM and the audio processor. Both of these devices follow the Phillips I<sup>2</sup>C bus protocol. Appendix 4 contains the details on how to configure the SSPB system for I<sup>2</sup>C compatible cycles, and also information on the clock and audio processor register maps.

# CHAPTER 3

### THE PANDORA CHIPS

They're something that I've never seen before

-*R*.*E*.*M*.

The Amiga 3000+ system is supported by a new Amiga gcaphics chip set, called the Pandora, or Advanced Amiga, chip set. This system greatly enhances the Amiga's video display capabilities, while remaining upward compatible with the Amiga ECS chip set, and retaining all of the graphics features unique to previous Amiga systems.

#### 3.1 Basic Description

The Pandora chip set consists of three full custom LSI chips, working together as a single unit. Alice, based directly on the 2MB ECS Agnus chip, is the main Amiga chip bus controller. It is responsible for generating video and memory timing for the other chips, and it contains bimmer and copper units. While Alice is still a 16 bit chip, it now can direct 32 bit and/or double speed transactions on the Chip bus, and is simpler to interface to the A3000 style 32 bit Chip memory bus. Paula is the chip responsible for 8-bit audio output, floppy disk and RS-232 serial I/O, and potentiomenter inputs. The Paula used in the Pandora chip set is the same Paula used in classic and ECS Amiga chip sets.

Completely new for Pandora is the Lisa. Lisa is a new full custom design, a replacement for Denise. Implemented in 1.5 $\mu$ m CMOS, Lisa has a 32 bit Chip bus interface, and with 80ns DRAM, double fetch cycles can fetch 64 bits of data in a single Chip bus cycle, a factor of four improvement over classic and ECS video fetch cycles. The Lisa chip output is 24 bits of digital

RGB video. High quality RBG analog output from the Lisa digital video is generated by an off-the-shelf video DAC, which is currently the Analog Devices ADV7120 Triple 8-bit Video DAC. A summary of Pandora features includes:

- 32 bit wide data bus supports input of 32-bit wide bitplane data and allows doubling of memory bandwidth. Additional doubling of bandwidth can be achieved by using Fast Page Mode RAM. The same bandwidth enhancements are available for sprites. Also the maximum number of bitplanes useable in all modes is increased to eight.

- The Color Palette has been expanded to 256 colors deep and 25 bits wide (8 red, 8 green, 8 blue, 1genlock). This permits display of 256 simultaneous colors in all resolutions. A palette of 16,777,216 colors is available in all resolutions.

- 28Mhz clock input to Lisa allows for cleaner definition of HIRES and SHRES pixels. Alice's clock generator is synchronized by means of Lisa's 14MHz and SCLK outputs.

- A new register bit allows sprites to appear in the screen border regions..

- A bitplane mask field of 8 bits allows an address offset into the color palette. Two 4-bit mask fields do the same for odd and even sprites.

- In Dual Playfield modes, two 4-bitplane playfields are now possible in all resolutions.

- Two extra high-order playfield scroll bits allow seamless scrolling of up to 64 bit wide bitplanes in all resolutions. Resolution of bitplane scroll, display window, and horizontal sprite position has been improved to 35ns in all resolutions.

- A new 8 bitplane HAM mode has been created, 6 bits for colors and 2 for control bits. All HAM modes are available in all resolutions (not just LORES as before).

- A reset input pin has been added, which resets all the bits contained in registers that were new for ECS or LISA.

- Sprite resolution can be set to LORES, HIRES, or SHRES, independent of bitplane resolution.

- Attached Sprites are now available in all resolutions.

- Hardware Scan Doubling support has been added for bitplanes and sprites. This is intended to allow 15KHz screens to be intelligently displayed on a 31KHz monitor, and share the display with 31KHz screens.

While its possible to fully describe each and every display mode, this isn't really necessary. First of all, there are now an awful lot of combinations available. Since the A3000+ supports the full bandwidth Pandora Chip RAM, all display modes are possible. Basically, all display modes, interlacing, and resolution are independent of one another. Display modes can be straight bitmap, from 1 to 8 bitplanes. There is also 6 bitplane Extra HalfBright, and both 6 and 8 bitplane Hold and Modify. Resolutions are a combination of pixel speed and horizontal refresh. Pixels can be 140ns, 70ns, or 35ns. Horizontal refresh rates are usually 15.7kHz or 31kHz. Some of the combinations are given in Appendix 5.

#### **3.2 New Features**

There are quite a few new features in the Pandora chip set. The basic details of these features are described here. A more complete explanation is available in the internal Commodore document *Functional Specification for the Advanced Amiga Chip Set (AA)*, by Bob Raible and Spenser

Shanson, where much of this chapter originates. An external version of this document, along with system software changes dealing with the Pandora changes, will certainly be made available as the need for additional information arises.

#### 3.2.1 Bitplanes

There are now 8 bitplanes instead of 6. In single playfield modes they can address 256 colors instead of just 64. As long as the memory architecture supports the bandwidth, all 8 bitplanes are available in all 3 resolutions. In the same vein, 4+4 bitplane dual playfield is available in all 3 resolutions, unless bitplane scan-doubling is enabled, in which case both playfields share the same bitplane modulus register. Bits 15 thru 8 of BPLCON4 comprise an 8 bit mask for the 8 bit bitplane address, XOR'ing the individual bits. This allows the copper to exchange color maps with a single instruction. BPLCON1 now contains an 8 bit scroll value for each of the playfields. Granularity of scroll now extends down to 35nSec.(1 SHRES pixel), and scroll can delay playfield thru 32 bus cycles. Bits BPAGEM and BPL32 in new register FMODE control size of bitplane data in BPL1DAT thru BPL8DAT.

| Six Bit HAM     |                 |                                    |        |                                  |  |  |  |  |  |  |

|-----------------|-----------------|------------------------------------|--------|----------------------------------|--|--|--|--|--|--|

| BP <sub>6</sub> | BP5             | RED                                | GREEN  | BLUE                             |  |  |  |  |  |  |

| 0               | 0               | select new base register (1 of 16) |        |                                  |  |  |  |  |  |  |

| 0               | 1               | hold                               | hold   | modify                           |  |  |  |  |  |  |

| 1               | 0               | modify                             | hold   | hold                             |  |  |  |  |  |  |

| 1               | 1               | hold                               | modify | hold                             |  |  |  |  |  |  |

|                 |                 |                                    |        |                                  |  |  |  |  |  |  |

| Eight Bit HAM   |                 |                                    |        |                                  |  |  |  |  |  |  |

| <u>BP</u> 2     | $\mathbf{BP}_1$ | RED                                | GREEN  | BLUE                             |  |  |  |  |  |  |

| 0               | 0               | select new base register(1 of 64)  |        |                                  |  |  |  |  |  |  |

| 0               | 1               | hold                               | hold   | modify                           |  |  |  |  |  |  |

| 1               | 0               | modify                             | hold   | hold                             |  |  |  |  |  |  |

| 1               | 1               | hold                               | modify | hold                             |  |  |  |  |  |  |

| 1               |                 |                                    |        | Table 3-1: Pandora HAM Encodings |  |  |  |  |  |  |

The old 6 bitplane HAM (Hold And Modify) mode, unlike before, works in HIRES and SHRES resolutions. As before bitplanes 5 and 6 control its function. There is a new 8 bitplane HAM mode. This mode is invoked when BPU field in BPLCON0 is set to 8, and HAMEN is set.

Bitplanes 1 and 2 are used as control bits analagous to the function of bitplanes 5 and 6 in 6 bitplane HAM mode. Since only 6 bitplanes are available for modify data, the data is placed in the 6 MSB. The 2 LSB are left unmodified, which allows creation of all 16,777,216 colors simultaneously, assuming one had a large enough screen and picked one's base registers judiciously. This HAM mode also works in HIRES and SHRES modes. Pandora HAM modes are summerized in *Table 3-1*.

For compatibility reasons EHB mode remains intact. Its existence is rather moot in that we have more than enough colors in the color table to replace its functionality. As before, EHB is invoked whenever SHRES=HIRES=HAMEN=DPF=0, and BPU=6. Please note that starting with ECS DENISE there is a bit in BPLCON2 which disables this mode(KILLEHB).

Bits PF2OF2,1,0 in BPLCON3 determine second playfield's offset into the color table. This is now necessary since playfields in DPF mode can have up to 4 bitplanes. Offset values are as defined in register map.

BSCAN2 bit in FMODE enables bitplane scan-doubling. When V0 bit of DIWSTRT matches V0 of vertical beam counter, BPL1MOD contains the modulus for the display line, else BPL2MOD is used. When scan-doubled both odd and even bitplanes use the same modulus on a given line, whereas in normal mode odd bitplanes used BPL1MOD and even bitplanes used BPL2MOD. As a result Dual Playfield screens will probably not display correctly when scan-doubled.

#### 3.2.2 Sprites

Bits SPAGEM and SPR32 in FMODE determine whether size of sprite load data in SPR0DATA(B) thru SPR7DATA(B) is 16, 32, or 64 bits, analagous to bitplanes. BPLCON3 contains several bits relating to sprite behavior. SPRES1 and SPRES0 control sprite resolution, whether they conform to the ECS standard, or override to LORES, HIRES, or SHRES. BRDRSPRT, when high, allows sprites to be visible in border areas. ESPRM7 thru ESPRM4 allow relocation of the even sprite color map. OSPRM7 thru OSPRM4 allow relocation of the odd sprite color map. In the case of attached sprites OSPRM bits are used.

SSCAN2 bit in FMODE enables sprite scan-doubling. When enabled, individual SH10 bits in SPRxPOS registers control whether or not a given sprite is to be scan-doubled. When V0 bit of SPRxPOS register matches V0 bit of vertical beam counter, the given sprite's DMA is allowed to proceed as before. If they don't match, then sprite DMA is disabled and Lisa reuses the sprite data from the previous line. Sprite vertical start and stop positions must be of the same parity, i.e. both odd or both even.

#### 3.2.3 Video

The BYPASS bit in BPLCON0 allows prioritized color address to bypass the color table and exit Lisa on R(7:0) bus. SOGEN bit in BPLCON2 determines state of Sync-On-Green (SOG) output. This is intended to signal the Video DAC chip (KELLY) to superimpose the composite sync signal onto the analog green output. Horizontal blanking registers HBSTART and HBSTOP have been added to Lisa, eliminating the need for an external blanking input pin. There is now a BLANK output which allows the analog level for blanking to be different than black. BRDRBLNK bit in BPLCON3 allows the background to be BLACK and not the contents of COLOR00 (the name of this bit is now a misnomer, but there are no plans to change it). Note also that the 28MHz output of Lisa provides a pixel-synchronous clock, which will make scan conversion devices much easier to design.

#### **3.2.4** Compatibility

System reset initializes the all new Pandora registers, including BPLCON3, BPLCON4, CLXCON2, DIWHIGH, and FMODE. The ECSENA bit (formerly ENBPLCN3) is used to disable those register bits that are never accessed by old copper lists, and in addition are required by old-style copper lists to be in their default settings. Specifically, a low in ECSENA forces the bits BRDRBLNK, BRDNTRAN, ZDCLKEN, EXTBLKEN, and BRDRSPRT to their default states. When ECSENA is high again, the former settings return. CLXCON2 is reset by a write to CLXCON, so that old game programs will be able to correctly detect collisions. DIWHIGH is reset by writes to DIWSTRT or DIWSTOP. This interlock is inherited from ECS Denise.

#### 3.2.5 Genlock Stuff

Lots of new genlock features were added to ECS Denise and are carried over to Lisa. ZDBPEN in BPLCON2 allows any bitplane, selected by ZDBPSEL2,1,0, to be used as a transparency mask (ZD pin mirrors contents of selected bitplane). ZDCTEN disables the old COLOR00 is transparent mode, and allows the bit31 position of each color in the color table to control transparency. ZDCLKEN generates a 14MHz clock synchronized with the video data that can be used by video post-processors. Finally, BRDNTRAN in BPLCON3 generates an opaque border region which can used to frame live video.

| BANK <sub>2</sub>                 | BANK1 | BANK <sub>0</sub> | Color Address Range |  |  |  |

|-----------------------------------|-------|-------------------|---------------------|--|--|--|

| 0                                 | 0     | 0                 | COLOR00 - COLOR1F   |  |  |  |

| 0                                 | 0     | 1                 | COLOR20 - COLOR3F   |  |  |  |

| 0                                 | 1     | 0                 | COLOR40 - COLOR5F   |  |  |  |

| 0                                 | 1     | 1                 | COLOR60 - COLOR7F   |  |  |  |

| 1                                 | 0     | 0                 | COLOR80 - COLOR9F   |  |  |  |

| 1                                 | 0     | 1                 | COLORA0 - COLORBF   |  |  |  |

| 1                                 | 1     | 0                 | COLORC0 - COLORDF   |  |  |  |

| 1                                 | 1     | 1                 | COLORE0 - COLORFF   |  |  |  |

| Table 3-2: Lisa Color Map Banking |       |                   |                     |  |  |  |

#### **3.2.6 Color Lookup Table**

The color table has grown from 32 13-bit registers to 256 25-bit registers. Several new register bits have been added to BPLCON3 to facilitate loading the table with only 32 register addresses. LOCT, selects either the 16 MSB or LSB for loading. Loading the MSB always loads the LSB as well for compatibility, so when 24 bit colors are desired load LSB after MSB. BANK2,1,0 select 1 of 8 32 address banksfor loading, as shown in *Table 3-2*. The RDRAM bit in BPLCON2 causes Lisa to interpret all color table accesses as reads.

There is no longer any need to "scramble" SHRES color table entries. This artifice is no longer required and people who bypass ECS graphics library calls to do their own 28MHz graphics are to be pointed at and publicly humiliated.

#### 3.2.7 Collision

A new register CLXCON2 contains 4 new bits. ENBP7 and ENBP6 are the enable bits for bitplanes 7 and 8, respectively. Similarly, MVBP7 and MVBP8 are their match value bits. CLXDAT is unchanged.

#### **3.2.8 Horizontal Comparators**

All programmable comparators with the exception of VHPOSW have 35nS resolution. DIWHIGH, HBSTRT, HBSTOP, SPRCTL, BPLCON1. BPLCON1 has additional high-order bits as well. Note that the horizontal bit position representing 140nS resolution has been changed to 3rd least significant bit, where before it used to be a field's LSB. For example, bit 00 in BPLCON1 used to be named PF1H0 and now it's called PF1H2.

#### 3.2.9 Mouse/Joysticks

A two pin serial mouse interface replaces the 4 pin CCK multiplex scheme. This change is transparent to the programmer and allows 8 extra bits to be shifted in as well. These are displayed in the 8 MSB of LISAID and are intended for hardware configuration information. The mouse counters are updated only 1/16 as often as before (223 kHz), but this should be transparent to the user.

#### 3.2.10 Coercion of 15 kHz to 31 kHz

Lisa contains hardware mechanisms to aid in properly displaying 15 kHz and 31 kHz viewports together on the same 31 kHz display. Lisa can globally set sprite resolution to LORES, HIRES, or SHRES. Lisa will ignore SH10 compare bit in SPRxPOS when scan-doubling, thereby allowing Alice to use these bits to individually set scan-doubling.

## **CHAPTER 4**

## THE DSP3210 SUBSYSTEM

A live wire; barely a beginner but just watch that lady go! -Van Halen

The WE® DSP3210 is a floating-point digital signal processor, extremely well suited for use as a coprocessor in a microcomputer system such as the A3000+. The DSP3210 will speed up many of the things currently done on Amigas, and provide capabilities far beyond those built into current generation Amiga systems.

#### 4.1 WE® DSP3210 Overview

The DSP3210 is a floating-point digital signal processor, capable of running up to four memory accesses per instruction cycle, and up to 12.5 million instructions per second and 25 million floating-point operations per second. The DSP3210 architecture seeks to eliminate the problems that plagued earlier digital signal processors used as graphics, sound, and general signal coprocessors in a microcomputer environment. Rather than being limited to a few hundered bytes of on-chip RAM and a few thousand bytes of off-chip RAM, the DSP3210 couples 8K of very fast on-chip RAM with full 32-bit bus master capability, allowing it access to all 32-bit memory in the A3000+. Additionally, the AT&T Visable Caching Operating System<sup>®</sup> (VCOS) provides a realtime multitasking kernel for the DSP3210. This allows applications to use the DSP3210 as freely and as easily as they would use the host processor; within the limits of available processor time, no one application can tie up the DSP3210. Also, since VCOS supports multiple DSP3210s, even processor saturation may in time be solved with additional expansion hardware.

#### 4.2 DSP System Configuration

The basic DSP3210 exists as a normal motherboard bus master, with the highest DMA priority in the A3000+ system. It can run full speed 68030 compatible cycles, including burst-mode to motherboard and Zorro III expansion memory. Since the DSP is not register mapped, the communications protocol between it and the host processor is mainly an agreement in software. The system hardware provides a special DSP reset line which hold the DSP off the bus until the host processor has time to initialize the communications protocol. This reset line is controlled via a register in the Gary+ chip. Once the DSP is up and running, communcations between it and the host processor are helped by the ability to interrupt one another, via the Coprocessor Communication Register, from the host processor side (described in the System Controls chapter), and the DSP3210's BIO port., from the DSP3210 point of view.

The DSP3210 serves two main functions; that of a simple mathematics and signal processing resource, and that of an I/O processor. As a signal processing resource, applications programs can, though the Amiga-VCOS interface, run DSP3210 programs for a variety of jobs. It's also possible that software will be created to use the DSP transparently to the application; a high-level mathematics library is one example of this. Most number processing applications are scheduled under VCOS as non-realtime jobs.

For I/O processing, the DSP3210 has a high speed serial bus which can access the internal RAM via transparent DMA. The A3000+ provides a telepone line CODEC with telephone interface, and a stereo Hi-Fi audio codec with line, microphone, and headphone interfaces. Most I/O interaction, such as realtime audio and modem/FAX applications are scheduled under VCOS as realtime jobs.

#### **4.2.1 DSP Memory Map Differences**

While the DSP3210 shares the 32-bit linear address space of the A3000+ host processor, its internal resources are mapped over a small area of A3000+ memory, as shown in *Figure 4-1*. The DSP3210 can't access the memory "beneath" its on-chip resources, and the host processor can't access the DSP3210 on-chip resources. The main on-chip resources are Boot ROM (1K), on-chip I/O (1K), on-chip RAM (8K), and reserved area (54K). Note that the A3000+ system configures the DSP3210 to power up in  $\mu$ Computer mode, causing the on-chip resources to be located from \$0000000-\$0000FFFF. The alternate  $\mu$ Processor mode will cause the on-chip resources to be located from \$50030000-\$5003FFFF.

The other main difference in memory mapping is that the DSP3210 doesn't dynamically size its bus. The A3000+ support logic allows it to communicate with both synchronous and asynchronous 32-bit resources. It cannot, however, access 8 or 16 bit devices, such as some I/O registers, all custom chip control registers, and any Zorro II device. The system hardware is designed to send the DSP3210 a bus error if it attempts access of any non-32 bit wide port. Normally, the DSP is expected to need access only to RAM in any case, and Fast RAM at that most of the time. It should offload any external I/O processing to the host processor.

Figure 4-1: DSP3210 Internal Memory Map

#### 4.2.2 The DSP Reset Mechanism

Since the DSP comes up in  $\mu$ Computer mode, the Boot ROM is used for reset. The A3000+ sets things up such that the DSP3210 will expect to execute code starting at \$0001000. In order to let the DSP out of reset, the host processor will have to assure that this location contains the necessary DSP boot code. If this memory already contains something, it'll be necessary to first disable interrupts, save off whatever is at \$00010000, move the initialization code to \$00010000, enable the DSP via the Gary+ DSPRST register, wait on a signal (not an interrupt, these are disabled!) from the DSP indicating its through with the initialization code, then restore \$00010000, and finally enable interrupts again. This procedure shouldn't be anywhere nearly as nasty as it sounds, and it only needs to be done once, right after reset.

Typical initialization will go something like this. The DSP wakes up and starts running code at \$00010000. This code will more than likely transfer another chunk of code into the DSP's internal memory. The DSP will complete the transfer, jump to the internal code, and then signal the host processor, probably via a memory based semaphore, that it's done with the initialization code. This internal code will, at the least, allow the DSP to accept commands from the host processor. Initially, the DSP will wait for an interrupt. In a real system, interrupts will come from I/O as well as from host processor communications, of course. When the DSP gets a host attention interrupt, it'll go out to an agree-upon command buffer in external memory and figure out just what the host wants. Once it finishes the host task, it may notify the host that the task is complete, again via interrupt.

#### 4.2.3 The BIO Port

The A3000+ system configures the DSP3210 Bit I/O (BIO) port for several system support functions. The port-line relative mapping is shown in *Figure 4-1*. The first two bits are assigned to the telephone line CODEC. The Ring Indicator bit is an input from an optoisolator in the telephone line interface, which indicates to the DSP3210 that the phone is ringing. The next bit, the Hook bit, is an output used to hang up or pick up the phone line. The bit after that, bit two, is currently reserved.